# MAX32630 Rev B

User Guide UG6349; Rev 0; 10/16

# Abstract

The MAX32630 User Guide is targeted to hardware, embedded firmware and application developers. This guide provides information on how to use and configure the MAX32630 memory, peripherals and registers. For ordering information, complete feature sets, package information, and electrical specifications, refer to the MAX32630 data sheet.

## Contents

| 1     | Disc | Disclaimer and Revision History |                                                       |    |  |  |  |

|-------|------|---------------------------------|-------------------------------------------------------|----|--|--|--|

| 2 Ove |      | verview                         |                                                       |    |  |  |  |

|       | 2.1  | Core a                          | nd Architecture                                       | 6  |  |  |  |

|       |      | 2.1.1                           | Core Parameters                                       | 7  |  |  |  |

|       |      | 2.1.2                           | Generic Memory Map                                    | 8  |  |  |  |

|       |      | 2.1.3                           | AHB Buses                                             | 9  |  |  |  |

|       |      | 2.1.4                           | APB Buses                                             | 9  |  |  |  |

|       |      | 2.1.5                           | Private Peripheral Bus (CPU Core Internal)            | 9  |  |  |  |

|       |      | 2.1.6                           | Nested Vectored Interrupt Controller (NVIC)           | 10 |  |  |  |

|       |      | 2.1.7                           | Debug                                                 | 10 |  |  |  |

|       |      | 2.1.8                           | Trace                                                 | 11 |  |  |  |

|       | 2.2  | Power                           | Supplies and Modes                                    | 11 |  |  |  |

|       |      | 2.2.1                           | Supply Voltages                                       | 11 |  |  |  |

|       |      | 2.2.2                           | V <sub>DD18</sub> (Nominal 1.8V) Digital Power Supply | 11 |  |  |  |

|       |      | 2.2.3                           | V <sub>DDIO</sub> (1.8V to 3.6V) I/O Power Supply     | 11 |  |  |  |

|       |      | 2.2.4                           | V <sub>DDIOH</sub> (1.8V to 3.6V) I/O Power Supply    | 12 |  |  |  |

|       |      | 2.2.5                           | V <sub>DD12</sub> (Nominal 1.2V) Digital Power Supply | 12 |  |  |  |

|       |      | 2.2.6                           | V <sub>RTC</sub> (Nominal 1.8V) RTC Power Supply      | 12 |  |  |  |

|       |      | 2.2.7                           | V <sub>DDA</sub> (Nominal 1.8V) Analog Power Supply   | 12 |  |  |  |

|       |      | 2.2.8                           | V <sub>DDB</sub> (Nominal 3.3V) USB Power Supply      | 12 |  |  |  |

|       |      | 2.2.9                           | Low-Power Modes                                       | 12 |  |  |  |

|       |      | 2.2.10                          | Power Supply Monitoring                               | 13 |  |  |  |

|       | 2.3  | Clock                           | Sources                                               | 13 |  |  |  |

|       |      | 2.3.1                           | Internal 96MHz Relaxation Oscillator                  | 13 |  |  |  |

|       |      | 2.3.2                           | Internal 4MHz RC Oscillator                           | 13 |  |  |  |

|     | 2.3.3   | Internal 44MHz Relaxation Oscillator (Crypto Oscillator) | 13 |

|-----|---------|----------------------------------------------------------|----|

|     | 2.3.4   | RTC 32768Hz Crystal Oscillator                           | 14 |

| 2.4 | Memor   | y                                                        | 14 |

|     | 2.4.1   | Internal Flash Memory                                    | 14 |

|     | 2.4.2   | 8KB Instruction Cache                                    | 15 |

|     | 2.4.3   | Internal SRAM                                            | 15 |

|     | 2.4.4   | Peripheral Management Unit (PMU)                         | 16 |

|     | 2.4.5   | Info Block                                               | 16 |

|     | 2.4.6   | Flash Memory Controller                                  | 17 |

| 2.5 | Analog  | Peripherals                                              | 17 |

|     | 2.5.1   | 10-Bit ADC                                               | 17 |

|     | 2.5.2   | ADC Sample Limit Monitoring                              | 17 |

| 2.6 | Digital | Peripherals                                              | 17 |

|     | 2.6.1   | GPIO Pins w/Interrupt and Wakeup Capability              | 17 |

|     | 2.6.2   | 32-Bit Timer/Counters                                    | 18 |

|     | 2.6.3   | Windowed Watchdog Timers                                 | 18 |

|     | 2.6.4   | Low-Level Watchdog Timer                                 | 19 |

|     | 2.6.5   | Real Time Clock                                          | 19 |

|     | 2.6.6   | SPI Masters                                              | 19 |

|     | 2.6.7   | SPI Slave                                                | 19 |

|     | 2.6.8   | I <sup>2</sup> C Master                                  | 20 |

|     | 2.6.9   | I <sup>2</sup> C Slave                                   | 20 |

|     | 2.6.10  | UART                                                     | 20 |

|     | 2.6.11  | USB 2.0 Device Interface with Integrated Transceiver     | 21 |

|     | 2.6.12  | CRC Hardware Block with CRC16 and CRC32                  | 21 |

| 2.7 | Securit | y Features                                               | 21 |

|   |     | 2.7.1    | Trust Protection Unit (TPU)                   | 21 |

|---|-----|----------|-----------------------------------------------|----|

|   |     | 2.7.2    | AES Cryptographic Engine                      | 21 |

|   |     | 2.7.3    | Secure Key Storage Area                       | 22 |

|   |     | 2.7.4    | Code Scrambling                               | 22 |

| 3 | Mem | nory, Re | gister Mapping, and Access                    | 23 |

|   | 3.1 | Memor    | ry, Register Mapping, and Access Overview     | 23 |

|   | 3.2 | Standa   | Ird Memory Regions                            | 26 |

|   |     | 3.2.1    | Code Space                                    | 26 |

|   |     | 3.2.2    | SRAM Space                                    | 26 |

|   |     | 3.2.3    | Peripheral Space                              | 27 |

|   |     |          | 3.2.3.1 Peripheral APB Access                 | 27 |

|   |     |          | 3.2.3.2 Peripheral AHB Access                 | 29 |

|   |     | 3.2.4    | External RAM Space                            | 32 |

|   |     | 3.2.5    | External Device Space                         | 32 |

|   |     | 3.2.6    | System Area (Private Peripheral Bus)          | 32 |

|   |     | 3.2.7    | System Area (Vendor Defined)                  | 33 |

|   | 3.3 | Device   | -Specific Memory Regions                      | 33 |

|   |     | 3.3.1    | Instruction Cache Memory                      | 33 |

|   |     | 3.3.2    | AES Key and Working Space Memory              | 33 |

|   |     | 3.3.3    | MAA Key and Working Space Memory              | 33 |

|   | 3.4 | AHB B    | us Matrix and AHB Bus Interfaces              | 34 |

|   |     | 3.4.1    | Core AHB Interface - I-Code                   | 34 |

|   |     | 3.4.2    | Core AHB Interface - D-Code                   | 34 |

|   |     | 3.4.3    | Core AHB Interface - System                   | 34 |

|   |     | 3.4.4    | AHB Master - Peripheral Management Unit (PMU) | 34 |

|   |     | 3.4.5    | AHB Master - USB Endpoint Buffer Manager      | 34 |

|   | 3.5  | Flash ( | controller and Instruction Cache                          | 35 |

|---|------|---------|-----------------------------------------------------------|----|

|   |      | 3.5.1   | Overview                                                  | 35 |

|   |      | 3.5.2   | Flash Controller Operations                               | 35 |

|   |      |         | 3.5.2.1 Flash Write Operation                             | 35 |

|   |      |         | 3.5.2.2 Flash Page Erase Operation                        | 36 |

|   |      | 3.5.3   | Instruction Cache Controller Operations                   | 37 |

|   |      |         | 3.5.3.1 Enabling the Instruction Cache                    | 37 |

|   |      |         | 3.5.3.2 Flushing the Instruction Cache Contents           | 37 |

|   |      | 3.5.4   | Registers (FLC)                                           | 38 |

|   |      | 3.5.5   | Registers (ICC)                                           | 63 |

|   |      | 3.5.6   | Registers (TRIM)                                          | 67 |

| 4 | Syst | em Cor  | figuration and Management                                 | 71 |

|   | 4.1  | Recom   | mended Settings For Application Startup                   | 71 |

|   | 4.2  | Power   | Ecosystem and Operating Modes                             | 73 |

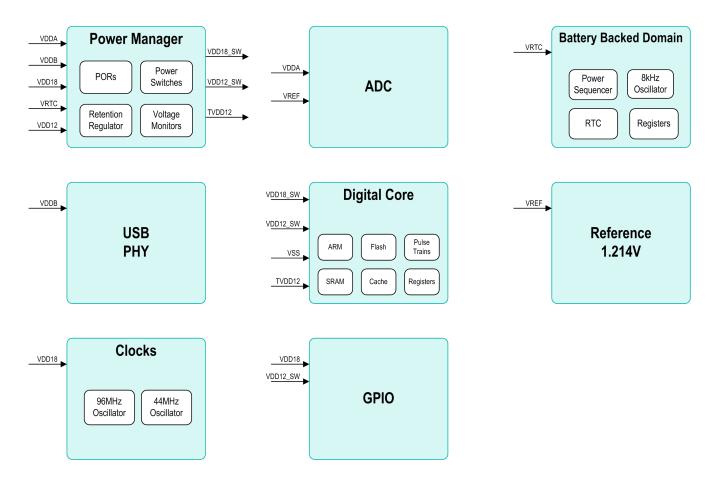

|   |      | 4.2.1   | Power Ecosystem                                           | 73 |

|   |      | 4.2.2   | Power Modes                                               | 75 |

|   |      |         | 4.2.2.1 Low Power Mode 0 (LP0:STOP)                       | 75 |

|   |      |         | 4.2.2.2 Low Power Mode 1 (LP1:STANDBY)                    | 75 |

|   |      |         | 4.2.2.3 Low Power Mode 2 (LP2:Peripheral Management Unit) | 75 |

|   |      |         | 4.2.2.4 Low Power Mode 3 (LP3:RUN)                        | 76 |

|   |      |         | 4.2.2.5 Wakeup Events from LP0:STOP and LP1:STANDBY       | 76 |

|   |      | 4.2.3   | Power State Matrix Control Options                        | 76 |

|   |      | 4.2.4   | Power Ecosystem                                           | 78 |

|   |      | 4.2.5   | Supply Voltage Monitors                                   | 79 |

|   |      | 4.2.6   | Power Sequencer                                           | 79 |

|   |      |         | 4.2.6.1 Power Mode Transitioning to Low Power Modes       | 79 |

|     | 4.2.7   | Registers   | s (PWRSEQ)                                | 80  |

|-----|---------|-------------|-------------------------------------------|-----|

|     | 4.2.8   | Registers   | s (PWRMAN)                                | 124 |

| 4.3 | Interru | pt Vector T | able                                      | 156 |

| 4.4 | Resets  | and Rese    | et Sources                                | 170 |

|     | 4.4.1   | System F    | Reset                                     | 171 |

|     |         | 4.4.1.1     | System Reset Pin (SRSTN)                  | 171 |

|     | 4.4.2   | Power-O     | n Reset (POR)                             | 171 |

|     | 4.4.3   | Power Se    | equencer Reset (PWRSEQ_Reset)             | 171 |

|     |         | 4.4.3.1     | RSTN (PWRSEQ_RSTN) Pin                    | 172 |

|     | 4.4.4   | VRTC Po     | wer On Reset (VRTC_POR)                   | 172 |

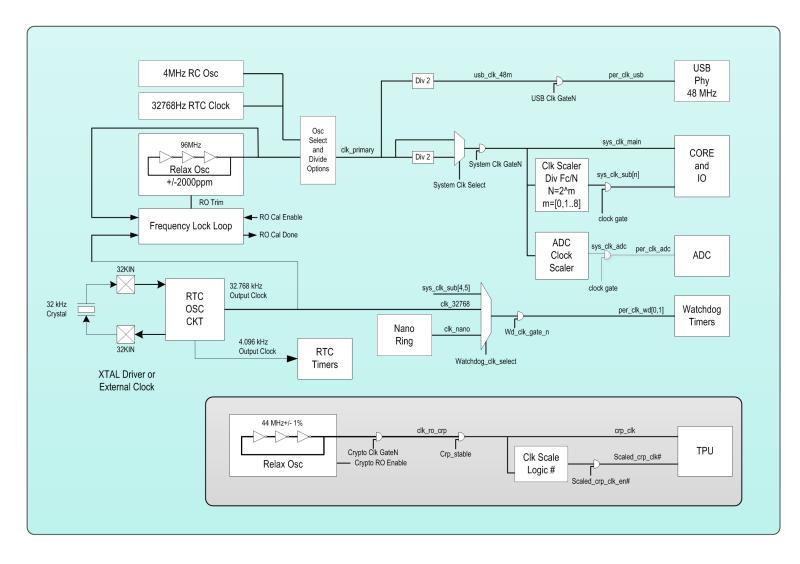

| 4.5 | Device  | Clock Sou   | urces and Configuration                   | 173 |

|     | 4.5.1   | Clock So    | urces                                     | 173 |

|     |         | 4.5.1.1     | System Relaxation Oscillator (96MHz)      | 175 |

|     |         | 4.5.1.2     | Internal RC Oscillator (4MHz)             | 177 |

|     |         | 4.5.1.3     | Configuring the Primary System Oscillator | 177 |

|     |         | 4.5.1.4     | Internal Crypto Oscillator (44MHz)        | 178 |

|     |         | 4.5.1.5     | 32768Hz Oscillator With External Crystal  | 178 |

|     | 4.5.2   | Clock Co    | nfiguration                               | 179 |

|     |         | 4.5.2.1     | System Clock Configuration                | 179 |

|     |         | 4.5.2.2     | Cryptographic Clock Configuration         | 180 |

|     |         | 4.5.2.3     | ADC Clock Configuration                   | 180 |

|     | 4.5.3   | Registers   | s (CLKMAN)                                | 182 |

| 4.6 | Window  | wed Watch   | ndog Timers                               | 219 |

|     | 4.6.1   | Overview    | /                                         | 219 |

|     | 4.6.2   | Clock So    | urce Selection and Gating                 | 219 |

|     | 4.6.3   | Watchdo     | g Timer Configuration                     | 220 |

|   |      |          | 4.6.3.1            | Enabling and Disabling the Watchdog Timer Counter      | 220 |

|---|------|----------|--------------------|--------------------------------------------------------|-----|

|   |      |          | 4.6.3.2            | Locking and Unlocking the Watchdog Timer Configuration | 221 |

|   |      | 4.6.4    | Watchdog           | Timer Operation                                        | 221 |

|   |      | 4.6.5    | Registers          | (WDT)                                                  | 222 |

|   | 4.7  | Low-Le   | evel Watch         | dog Timer                                              | 229 |

|   |      | 4.7.1    | Overview           |                                                        | 229 |

|   |      | 4.7.2    | Clock So           | urce and Gating                                        | 229 |

|   |      | 4.7.3    | Watchdog           | Timer Configuration                                    | 229 |

|   |      |          | 4.7.3.1            | Enabling and Disabling the Watchdog Timer Counter      | 230 |

|   |      |          | 4.7.3.2            | Locking and Unlocking the Watchdog Timer Configuration | 230 |

|   |      | 4.7.4    | Watchdog           | Timer Operation                                        | 231 |

|   |      |          | 4.7.4.1            | Configuring WDT2 to Wake Up the System from LP0 or LP1 | 231 |

|   |      |          | 4.7.4.2            | Configuring WDT2 to Reset the Power Sequencer          | 231 |

|   |      | 4.7.5    | Registers          | (WDT2)                                                 | 233 |

| 5 | GPIC | ) Pin Co | onfiguratio        | on and Peripheral Function Mapping                     | 239 |

|   | 5.1  | Pin Fu   | inction Map        | ping                                                   | 239 |

|   |      | 5.1.1    | GPIO Fui           | nction Mapping                                         | 240 |

|   | 5.2  | Genera   | al-Purpose         | I/O                                                    | 245 |

|   |      | 5.2.1    | Device Pi          | ns                                                     | 245 |

|   |      | 5.2.2    | Interrupts         |                                                        | 246 |

|   |      | 5.2.3    | Firmware           | Control                                                | 246 |

|   |      | 5.2.4    | Highest F          | Resistance Pullup/Pulldown Control                     | 248 |

|   |      |          |                    |                                                        |     |

|   |      |          | 5.2.4.1            | Enabling Highest Resistance Pullup Mode                | 249 |

|   |      |          | 5.2.4.1<br>5.2.4.2 | Enabling Highest Resistance Pullup Mode                |     |

|   |      | 5.2.5    | 5.2.4.2            |                                                        | 249 |

MAX32630 Rev B User Guide

|   |      | 5.2.5.2        | $\label{eq:Freezing} Freezing GPIO \ Output \ States \ During \ (LP3:RUN \rightarrow LP1:STANDBY \rightarrow LP3:RUN) \ Power \ Cycle \ \ldots \ $ | 250 |

|---|------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | 5.3  | GPIO Pins and  | Peripheral Mode Functions                                                                                                                                                                                                  | 251 |

|   |      | 5.3.1 P0/P1    | GPIO Function Options                                                                                                                                                                                                      | 252 |

|   |      | 5.3.2 P2/P3    | GPIO Function Options                                                                                                                                                                                                      | 253 |

|   |      | 5.3.3 P4/P5    | GPIO Function Options                                                                                                                                                                                                      | 254 |

|   |      | 5.3.4 P6/P7/   | P8 GPIO Function Options                                                                                                                                                                                                   | 255 |

|   | 5.4  | Registers (GPI | O)                                                                                                                                                                                                                         | 256 |

|   | 5.5  | Registers (IOM | IAN)                                                                                                                                                                                                                       | 287 |

| 6 | Dori | nheral Manager | ment Unit (PMU)                                                                                                                                                                                                            | 339 |

| Č | 6.1  | · · ·          | ······                                                                                                                                                                                                                     |     |

|   |      |                | ۱                                                                                                                                                                                                                          |     |

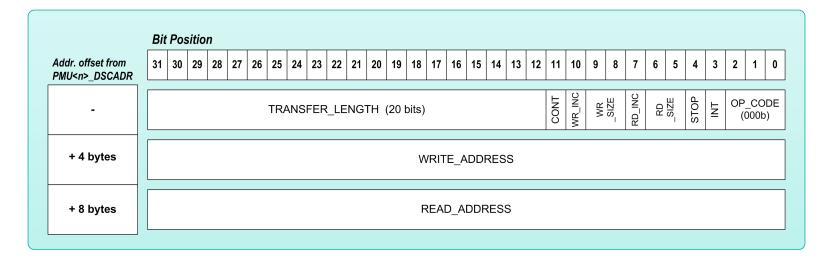

|   | 0.2  | 1              | Deration Descriptors                                                                                                                                                                                                       |     |

|   |      |                | and PMU Channel Start                                                                                                                                                                                                      |     |

|   |      |                |                                                                                                                                                                                                                            |     |

|   | 6.3  |                |                                                                                                                                                                                                                            |     |

|   | 0.3  |                |                                                                                                                                                                                                                            |     |

|   |      | 6.3.1.1        |                                                                                                                                                                                                                            |     |

|   |      |                |                                                                                                                                                                                                                            |     |

|   |      | 6.3.1.2        |                                                                                                                                                                                                                            |     |

|   |      | 6.3.1.3        |                                                                                                                                                                                                                            |     |

|   |      | 6.3.1.4        |                                                                                                                                                                                                                            |     |

|   |      | 6.3.1.5        |                                                                                                                                                                                                                            |     |

|   |      | 6.3.1.6        |                                                                                                                                                                                                                            |     |

|   |      | 6.3.1.7        |                                                                                                                                                                                                                            |     |

|   |      | 6.3.1.8        |                                                                                                                                                                                                                            |     |

|   |      | 6.3.1.9        |                                                                                                                                                                                                                            |     |

|   |      | 6.3.1.1        | 0 READ_ADDRESS                                                                                                                                                                                                             | 345 |

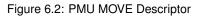

| 6.3.2 | WRITE D | Descriptor       | 346 |

|-------|---------|------------------|-----|

|       | 6.3.2.1 | OP_CODE          | 346 |

|       | 6.3.2.2 | INT              | 346 |

|       | 6.3.2.3 | STOP             | 347 |

|       | 6.3.2.4 | WRITE_METHOD     | 347 |

|       | 6.3.2.5 | WRITE_ADDRESS    | 347 |

|       | 6.3.2.6 | WRITE_VALUE      | 348 |

|       | 6.3.2.7 | WRITE_MASK       | 348 |

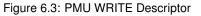

| 6.3.3 | WAIT De | escriptor        | 348 |

|       | 6.3.3.1 | OP_CODE          | 349 |

|       | 6.3.3.2 | INT              | 349 |

|       | 6.3.3.3 | STOP             | 349 |

|       | 6.3.3.4 | WAIT             | 349 |

|       | 6.3.3.5 | SEL              | 349 |

|       | 6.3.3.6 | WAIT_COUNT       | 349 |

|       | 6.3.3.7 | INT_MASK         | 349 |

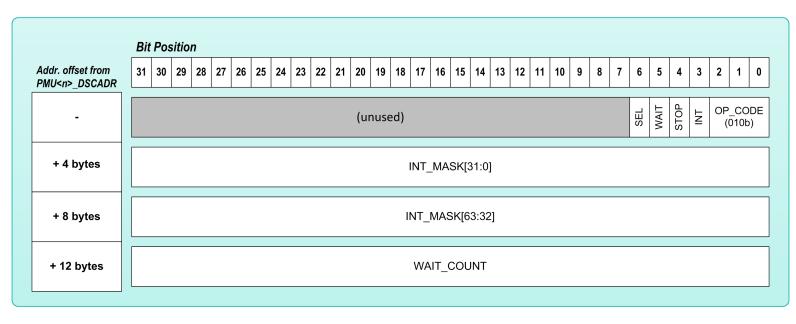

| 6.3.4 | JUMP D  | escriptor        | 355 |

|       | 6.3.4.1 | OP_CODE          | 356 |

|       | 6.3.4.2 | INT              | 356 |

|       | 6.3.4.3 | STOP             | 356 |

|       | 6.3.4.4 | NEXT_DSC_ADDRESS | 356 |

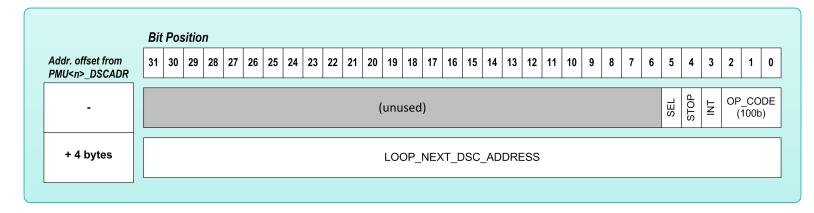

| 6.3.5 | LOOP D  | escriptor        | 356 |

|       | 6.3.5.1 | OP_CODE          | 357 |

|       | 6.3.5.2 | INT              | 357 |

|       | 6.3.5.3 | STOP             | 357 |

|       | 6.3.5.4 | SEL              | 357 |

|       | 6.3.5.5 | NEXT_DSC_ADDRESS        | 357 |

|-------|---------|-------------------------|-----|

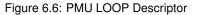

| 6.3.6 | POLL De | escriptor               | 358 |

|       | 6.3.6.1 | OP_CODE                 | 358 |

|       | 6.3.6.2 | INT                     | 359 |

|       | 6.3.6.3 | STOP                    | 359 |

|       | 6.3.6.4 | AND                     | 359 |

|       | 6.3.6.5 | POLL_ADDRESS            | 359 |

|       | 6.3.6.6 | DATA_EXPECTED           | 359 |

|       | 6.3.6.7 | DATA_MASK               | 359 |

|       | 6.3.6.8 | POLLING_INTERVAL        | 359 |

| 6.3.7 | BRANCH  | Descriptor              | 359 |

|       | 6.3.7.1 | OP_CODE                 | 360 |

|       | 6.3.7.2 | INT                     | 360 |

|       | 6.3.7.3 | STOP                    | 361 |

|       | 6.3.7.4 | AND                     | 361 |

|       | 6.3.7.5 | BR_TYPE                 | 361 |

|       | 6.3.7.6 | POLL_ADDRESS            | 362 |

|       | 6.3.7.7 | DATA_EXPECTED           | 362 |

|       | 6.3.7.8 | DATA_MASK               | 362 |

|       | 6.3.7.9 | BRANCH_NEXT_DSC_ADDRESS | 362 |

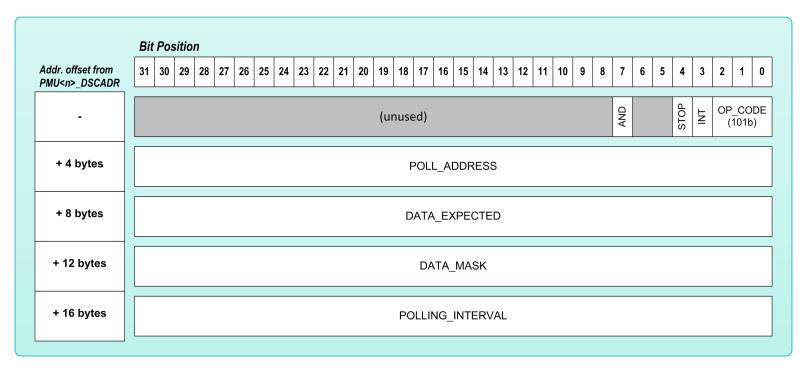

| 6.3.8 | TRANSF  | ER Descriptor           | 362 |

|       | 6.3.8.1 | OP_CODE                 | 363 |

|       | 6.3.8.2 | INT                     | 363 |

|       | 6.3.8.3 | STOP                    | 363 |

|       | 6.3.8.4 | RD_SIZE, WR_SIZE        | 364 |

|       | 6.3.8.5 | RD_INC                  | 364 |

|   |     |         | 6.3.8.6    | WR_INC                                                | 365 |

|---|-----|---------|------------|-------------------------------------------------------|-----|

|   |     |         | 6.3.8.7    | TRANSFER_LENGTH                                       | 365 |

|   |     |         | 6.3.8.8    | WRITE_ADDRESS                                         | 365 |

|   |     |         | 6.3.8.9    | READ_ADDRESS                                          | 365 |

|   |     |         | 6.3.8.10   | INT_MASK                                              | 365 |

|   |     |         | 6.3.8.11   | BURST_SIZE                                            | 367 |

|   | 6.4 | Regist  | ers (PMU)  |                                                       | 368 |

| 7 | Com | nmunica | tion Perip | herals                                                | 374 |

|   | 7.1 | 1-Wire  | Master .   |                                                       | 374 |

|   |     | 7.1.1   | 1-Wire M   | aster Overview                                        | 374 |

|   |     |         | 7.1.1.1    | References                                            | 374 |

|   |     | 7.1.2   | OWM Pir    | Configuration                                         | 374 |

|   |     | 7.1.3   | OWM Clo    | ock Selection and Clock Gating                        | 375 |

|   |     |         | 7.1.3.1    | 1-Wire Time Slot Period Generation                    | 376 |

|   |     | 7.1.4   | 1-Wire Pi  | rotocol                                               | 376 |

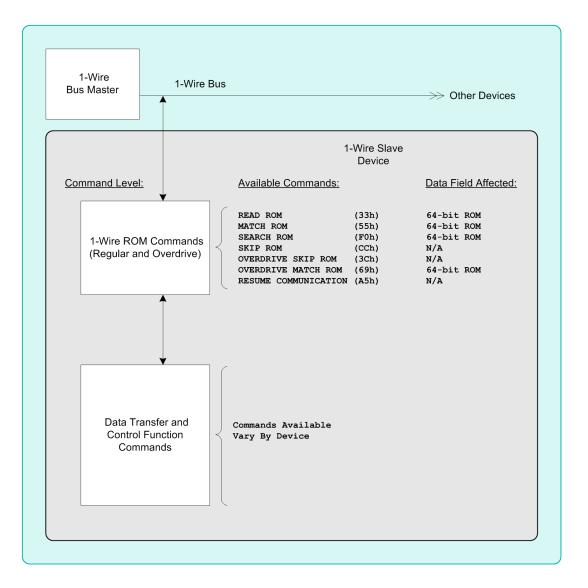

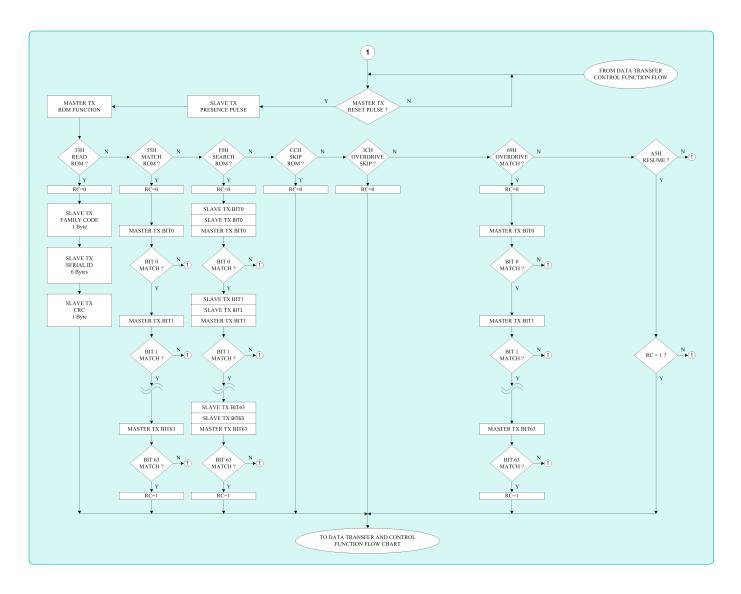

|   |     |         | 7.1.4.1    | Networking Layers                                     | 377 |

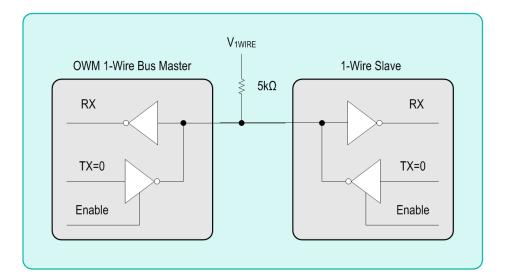

|   |     |         | 7.1.4.2    | Bus Interface (Physical Layer)                        | 377 |

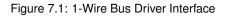

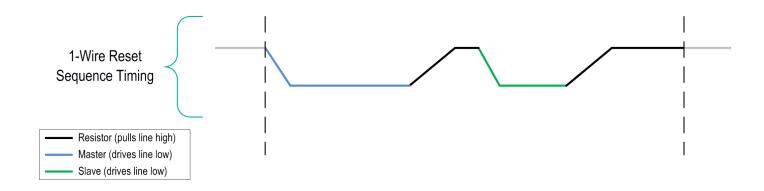

|   |     |         | 7.1.4.3    | Reset, Presence Detect and Data Transfer (Link Layer) | 378 |

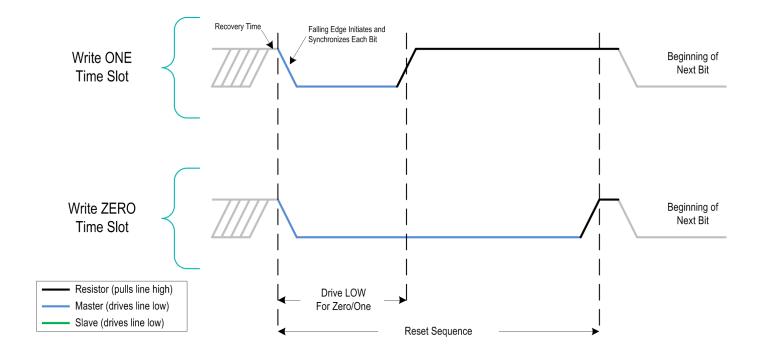

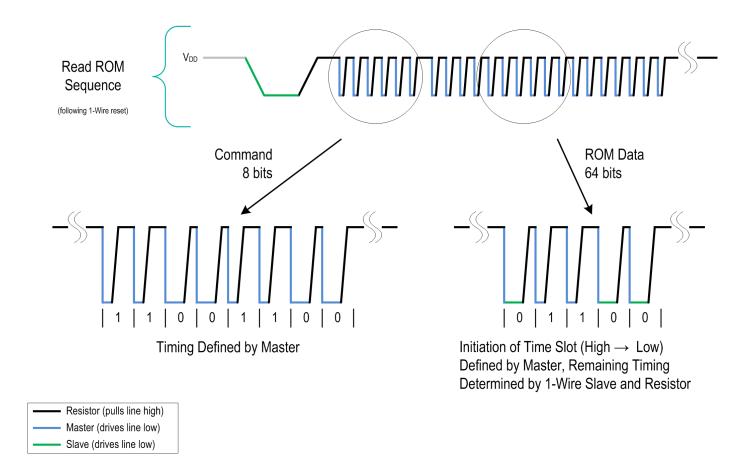

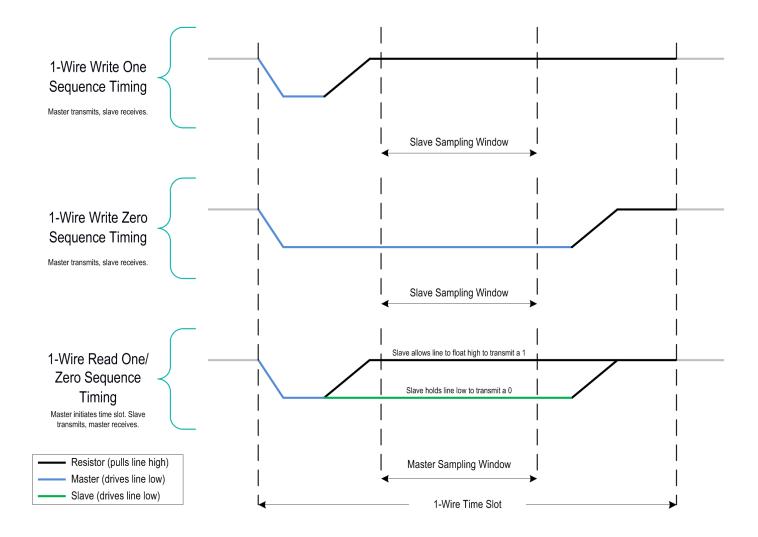

|   |     |         | 7.1.4.4    | Reading and Writing Bits                              | 379 |

|   |     |         | 7.1.4.5    | Standard Speed and Overdrive Speed                    | 383 |

|   |     |         | 7.1.4.6    | ROM Commands (Network Layer)                          | 385 |

|   |     | 7.1.5   | 1-Wire O   | peration                                              | 391 |

|   |     |         | 7.1.5.1    | Resetting the OWM 1-Wire Master                       | 391 |

|   |     |         | 7.1.5.2    | 1-Wire Data Writes                                    | 391 |

|   |     |         | 7.1.5.3    | 1-Wire Data Reads                                     | 392 |

|   |     | 7.1.6   | Registers  | s (OWM)                                               | 394 |

| 7.2 | I²C    |                                                  | 401 |

|-----|--------|--------------------------------------------------|-----|

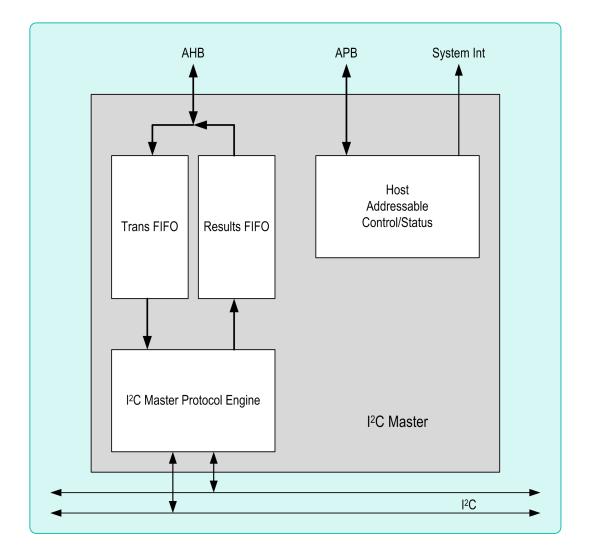

|     | 7.2.1  | Overview                                         | 401 |

|     | 7.2.2  | Features                                         | 401 |

|     | 7.2.3  | I <sup>2</sup> C Port and Pin Configurations     | 402 |

|     | 7.2.4  | I <sup>2</sup> C Master Operation                | 402 |

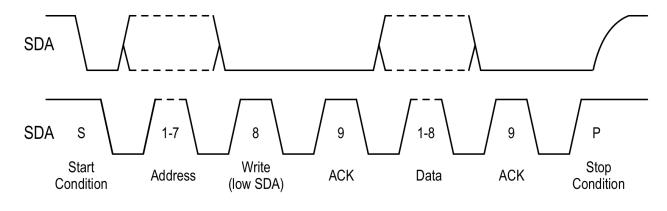

|     | 7.2.5  | Protocol                                         | 404 |

|     | 7.2.6  | Peripheral Clock Selection and Clock Gating      | 407 |

|     |        | 7.2.6.1 Peripheral Clock Frequency Selection     | 408 |

|     | 7.2.7  | Communication and Data Transfer                  | 409 |

|     |        | 7.2.7.1 FIFO-Based I <sup>2</sup> C Master       | 409 |

|     | 7.2.8  | I <sup>2</sup> C Interrupts                      | 410 |

|     | 7.2.9  | Module Clock Generation                          | 410 |

|     | 7.2.10 | Communication and Data Transfer                  | 411 |

|     |        | 7.2.10.1 I <sup>2</sup> C Mailbox                | 411 |

|     |        | 7.2.10.2 Slave Addressing                        | 412 |

|     |        | 7.2.10.3 Writing to a Single Mailbox Register    | 412 |

|     |        | 7.2.10.4 Writing to Multiple Mailbox Registers   | 413 |

|     |        | 7.2.10.5 Reading from a Single Mailbox Register  | 414 |

|     |        | 7.2.10.6 Reading from Multiple Mailbox Registers | 414 |

|     | 7.2.11 | Registers (I2CM)                                 | 416 |

|     | 7.2.12 | Registers (I2CS)                                 | 430 |

| 7.3 | SPIM . |                                                  | 450 |

|     | 7.3.1  | Overview                                         | 450 |

|     | 7.3.2  | SPIM Port and Pin Configurations                 | 452 |

|     |        | 7.3.2.1 Pin Layout Configuration                 | 452 |

|     | 7.3.3  | Clock Selection and Configuration                | 454 |

|     | 7.3.4  | lock Gating                                         | 155 |

|-----|--------|-----------------------------------------------------|-----|

|     | 7.3.5  | onfiguration Modes Overview                         | 155 |

|     |        | 3.5.1 Static Configuration                          | 155 |

|     |        | 3.5.2 Dynamic Configuration                         | 156 |

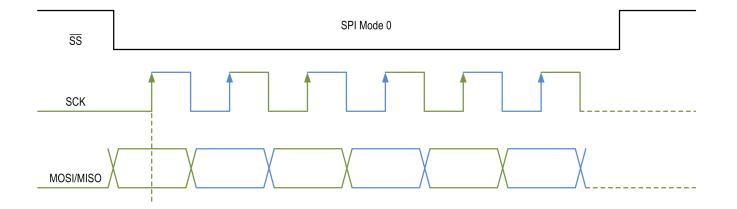

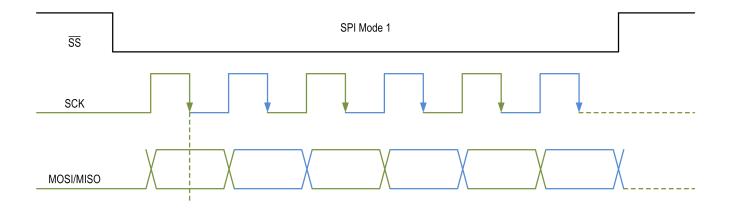

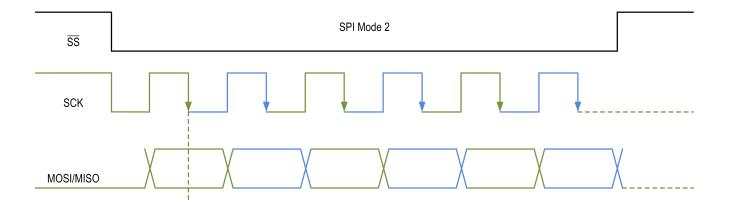

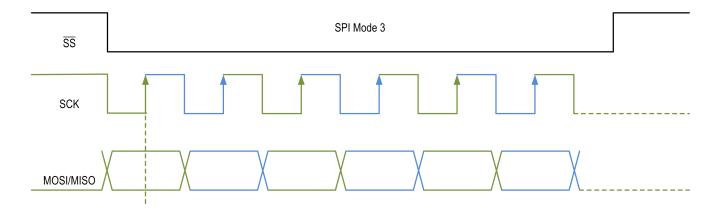

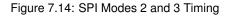

|     |        | 3.5.3 SPI Mode Selection (Clock Polarity and Phase) | 156 |

|     |        | 3.5.4 Serial Clock                                  | 158 |

|     |        | 3.5.5 Transaction Delay                             | 159 |

|     |        | 3.5.6 Page Size                                     | 159 |

|     | 7.3.6  | ommunication and Data Transfer                      | 160 |

|     | 7.3.7  | terrupts                                            | 162 |

|     | 7.3.8  | egisters (SPIM)                                     | 463 |

| 7.4 | SPIS . |                                                     | 181 |

|     | 7.4.1  | verview                                             | 181 |

|     | 7.4.2  | PIS Port and Pin Configurations                     | 181 |

|     | 7.4.3  | lock Selection and Configuration                    | 182 |

|     | 7.4.4  | egisters (SPIS)                                     | 183 |

| 7.5 | UART   |                                                     | 194 |

|     | 7.5.1  | verview                                             | 194 |

|     | 7.5.2  | ART I/O and Pin Configuration                       | 194 |

|     |        | 5.2.1 UART Interface Signals                        | 194 |

|     |        | 5.2.2 UART 0 Pin Configurations                     | 195 |

|     |        | 5.2.3 UART 1 Pin Configurations                     | 196 |

|     |        | 5.2.4 UART 2 Pin Configurations                     | 196 |

|     |        | 5.2.5 UART 3 Pin Configurations                     | 197 |

|     | 7.5.3  | ART Clock Configuration                             | 197 |

|     |        | 5.3.1 UART Common Clock Basis and Scaling           | 197 |

|     |        |                                                     |     |

|     |        | 7.5.3.2 UART Clock Gating Controls (Per Instance)     | 198 |

|-----|--------|-------------------------------------------------------|-----|

|     | 7.5.4  | Format and Baud Rate Selection                        | 199 |

|     | 7.5.5  | Transmitting and Receiving Data                       | 500 |

|     | 7.5.6  | Interrupts                                            | 500 |

|     | 7.5.7  | Hardware Flow Control                                 | 500 |

|     |        | 7.5.7.1 CTS (Clear To Send)                           | 500 |

|     |        | 7.5.7.2 RTS (Ready To Send)                           | 501 |

|     | 7.5.8  | Multidrop Mode Support                                | 501 |

|     | 7.5.9  | Registers (UART)                                      | 503 |

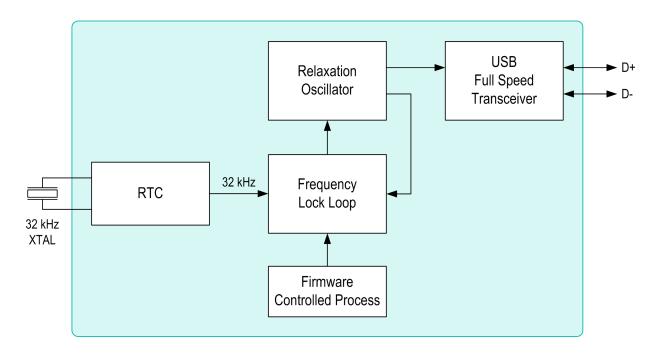

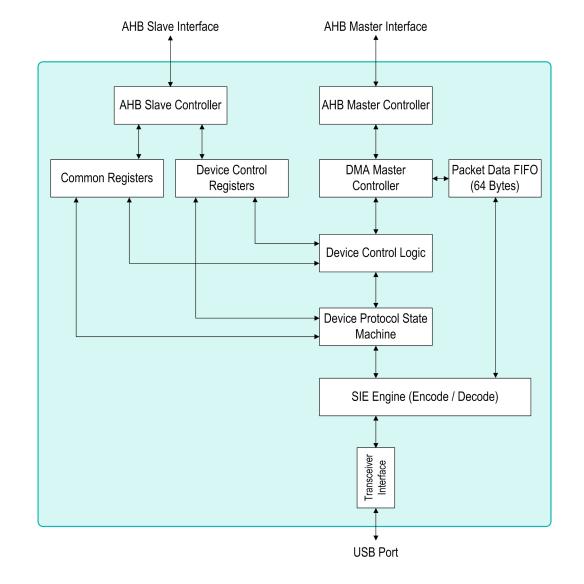

| 7.6 | USB D  | Device Interface                                      | 518 |

|     | 7.6.1  | Overview                                              | 518 |

|     | 7.6.2  | Operation                                             | 518 |

|     |        | 7.6.2.1 USB Reset Definitions                         | 518 |

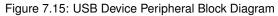

|     | 7.6.3  | USB Endpoints                                         | 520 |

|     |        | 7.6.3.1 Endpoint Control Register                     | 520 |

|     |        | 7.6.3.2 Endpoint Buffer Descriptor                    | 520 |

|     | 7.6.4  | Registers (USB)                                       | 522 |

| 7.7 | SPI XI | Ρ5                                                    | 544 |

|     | 7.7.1  | Overview                                              | 544 |

|     | 7.7.2  | SPIX Pin Configuration                                | 544 |

|     | 7.7.3  | External Memory Device Requirements for Use with SPIX | 545 |

|     | 7.7.4  | SPIX Memory                                           | 545 |

|     |        | 7.7.4.1 SPIX Memory Mapping                           | 545 |

|     |        | 7.7.4.2 SPIX External Memory Caching and Scrambling   | 547 |

|     |        | 7.7.4.3 SPIX Memory Access                            | 548 |

|     |        | 7.7.4.4 Configuring SPIX Memory Access                | 548 |

|   |      | 7.7.5    | SPIX Clock Selection and Clock Gating   | 549 |

|---|------|----------|-----------------------------------------|-----|

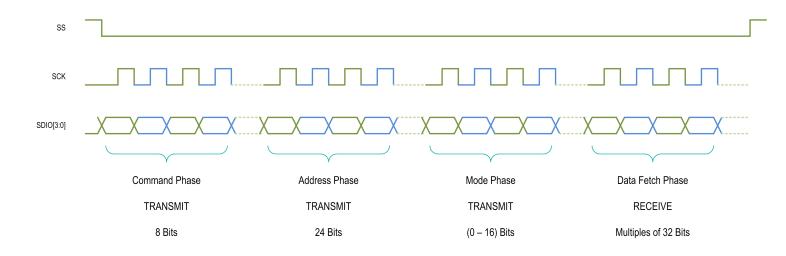

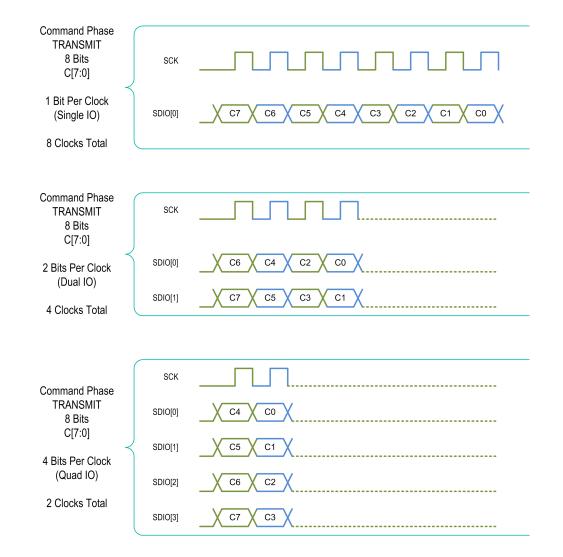

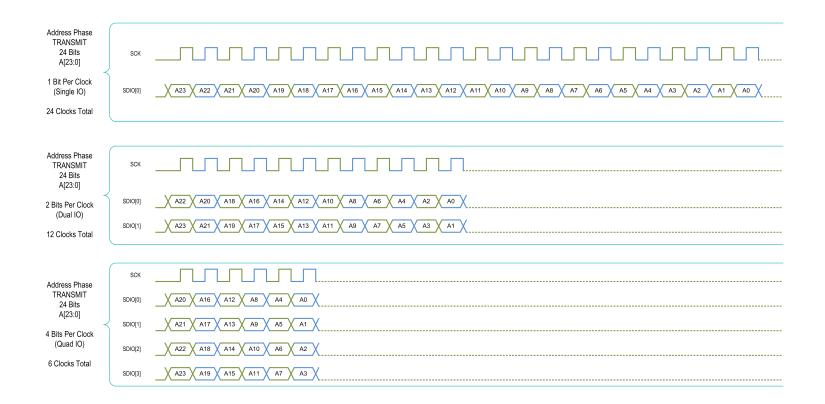

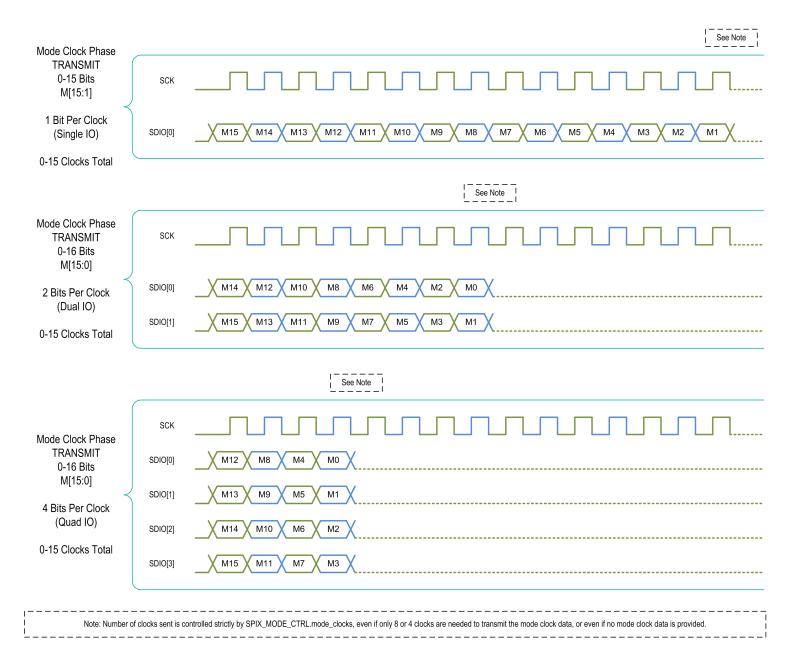

|   |      |          | 7.7.5.1 SPIX Protocol Format and Timing | 550 |

|   |      | 7.7.6    | SPIX Configuration                      | 550 |

|   |      | 7.7.7    | Registers (SPIX)                        | 558 |

| 8 | Ana  | log to D | igital Converter                        | 567 |

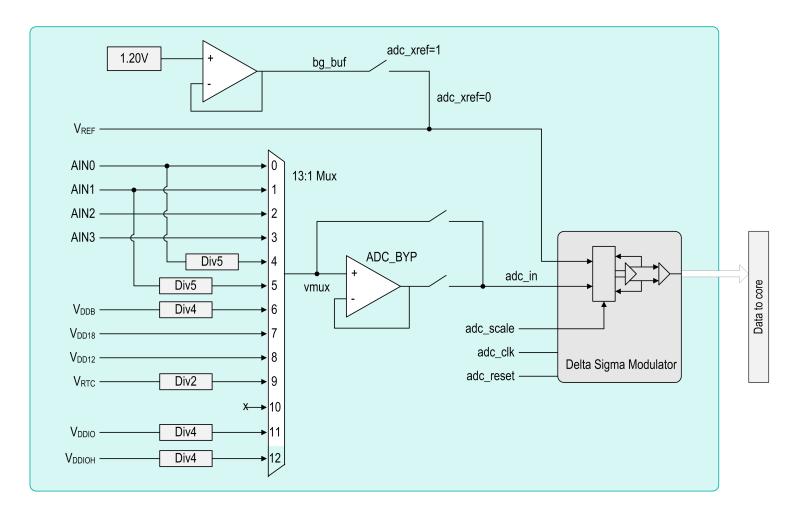

|   | 8.1  | Analog   | to Digital Converter Overview           | 567 |

|   | 8.2  | Analog   | to Digital Converter Architecture       | 567 |

|   | 8.3  | Analog   | to Digital Converter Operation          | 569 |

|   |      | 8.3.1    | Control Interface                       | 569 |

|   |      | 8.3.2    | Using an External Reference             | 569 |

|   | 8.4  | Analog   | to Digital Converter Configuration      | 569 |

|   |      | 8.4.1    | Power-Up Sequence                       | 570 |

|   |      | 8.4.2    | Conversion Process                      | 570 |

|   |      | 8.4.3    | Peripheral Clock Configuration          | 571 |

|   |      | 8.4.4    | Firmware Control of the ADC Sample Rate | 571 |

|   |      | 8.4.5    | Power-Down Sequence                     | 571 |

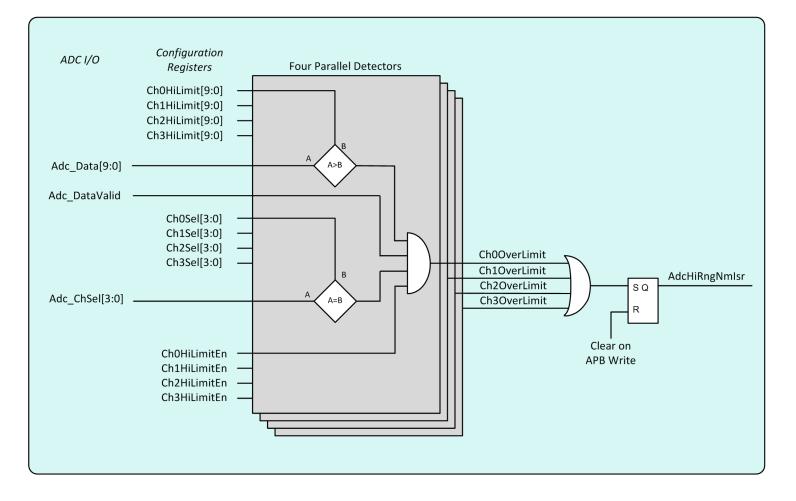

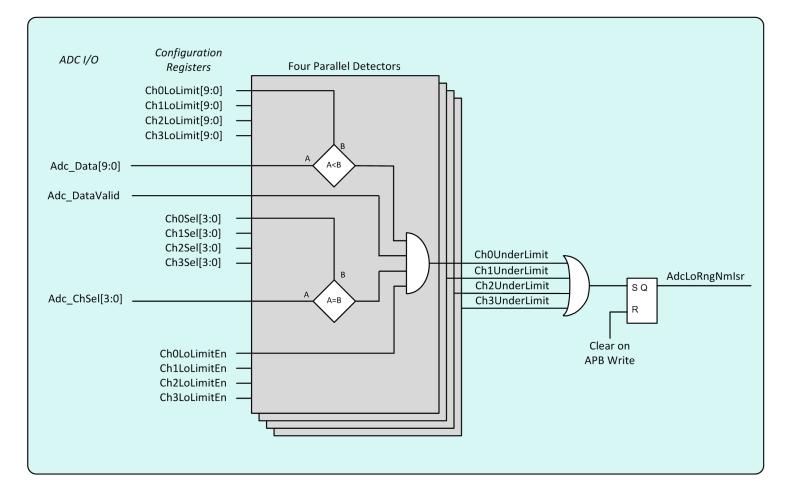

|   |      | 8.4.6    | ADC Data Limits                         | 571 |

|   |      | 8.4.7    | Data Value Equations                    | 574 |

|   | 8.5  | Registe  | ers (ADC)                               | 576 |

| 9 | Puls | e Train  | Engine                                  | 594 |

|   | 9.1  | Pulse 7  | Train (PT) Engine Overview              | 594 |

|   | 9.2  | Prereq   | uisites for Use                         | 595 |

|   |      | 9.2.1    | Pulse Train Register Mapping            | 595 |

|   |      | 9.2.2    | Pulse Train Peripheral Clock Generation | 596 |

|   |      | 9.2.3    | Pulse Train Peripheral Clock Gating     | 596 |

MAX32630 Rev B User Guide

|    |      | 9.2.4              | Pulse Train GPIO Mapping                         | 597 |

|----|------|--------------------|--------------------------------------------------|-----|

|    | 9.3  | Pulse <sup>-</sup> | Train Global Controls                            | 597 |

|    |      | 9.3.1              | Enabling and Disabling Pulse Train Engines       | 598 |

|    |      | 9.3.2              | Interrupt Controls for All Pulse Train Engines   | 598 |

|    |      | 9.3.3              | Synchronizing Pulse Train Instances              | 598 |

|    | 9.4  | Pulse <sup>-</sup> | Train Engine Operation                           | 599 |

|    |      | 9.4.1              | Default GPIO Output                              | 599 |

|    |      | 9.4.2              | Output Rate Control                              | 599 |

|    |      | 9.4.3              | Pulse Train Mode                                 | 599 |

|    |      | 9.4.4              | Pulse Train Loop Count                           | 600 |

|    |      | 9.4.5              | Pulse Train Loop Delay                           | 600 |

|    |      | 9.4.6              | Automatic Restart Mode                           | 601 |

|    |      | 9.4.7              | Square Wave Mode                                 | 602 |

|    | 9.5  | Regist             | ers (PT)                                         | 603 |

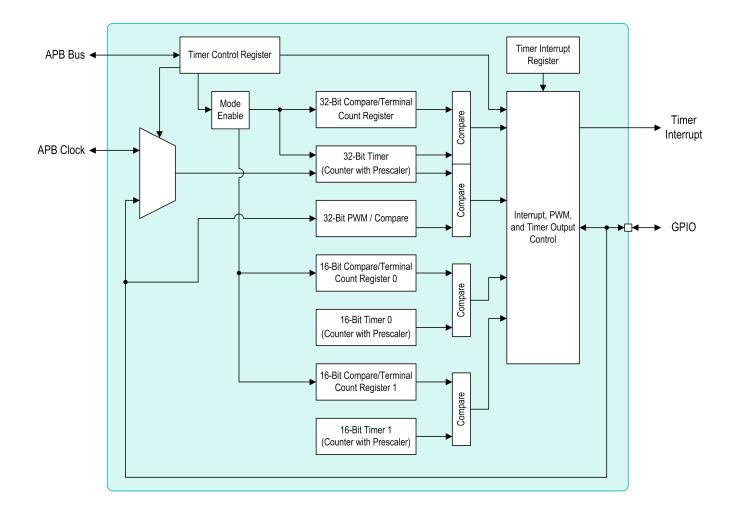

| 10 | Time | er/Coun            | ters                                             | 617 |

|    | 10.1 | Overvi             | ew                                               | 617 |

|    | 10.2 | Timer              | GPIO Mapping                                     | 619 |

|    |      | 10.2.1             | Configuring Timer Input Pins (32-bit Mode Only)  | 620 |

|    |      | 10.2.2             | Configuring Timer Output Pins (32-bit Mode Only) | 621 |

|    | 10.3 | 32-bit I           | Mode Timer Operation                             | 621 |

|    |      | 10.3.1             | One-Shot Mode (Output I/O)                       | 622 |

|    |      | 10.3.2             | Continuous Mode (Optional Output I/O)            | 623 |

|    |      | 10.3.3             | Counter Mode (Required Input I/O)                | 624 |

|    |      | 10.3.4             | PWM Mode (Required Output I/O)                   | 625 |

|    |      | 10.3.5             | Capture Mode (Required Input I/O)                | 626 |

|    |      | 10.3.6             | Compare Mode (Optional Output I/O)               | 628 |

|    |      | 10.3.7 Gated Mode (Required Input I/O)                | 629 |

|----|------|-------------------------------------------------------|-----|

|    |      | 10.3.8 Measurement Mode (Required Input I/O)          | 630 |

|    | 10.4 | 16-bit Mode Timer Operation                           | 631 |

|    |      | 10.4.1 One-Shot Mode                                  | 632 |

|    |      | 10.4.2 Continuous Mode                                | 633 |

|    | 10.5 | Registers (TMR)                                       | 635 |

| 11 | Real | Time Clock (RTC)                                      | 645 |

|    | 11.1 | Real Time Clock Overview                              | 645 |

|    |      | 11.1.1 Real Time Clock Features                       | 645 |

|    | 11.2 | RTC Resets                                            | 645 |

|    | 11.3 | RTC Interrupts                                        | 646 |

|    | 11.4 | RTC Configuration                                     | 647 |

|    |      | 11.4.1 Selecting the Timer Prescale Value             | 647 |

|    |      | 11.4.2 Setting the RTC Timer to a Zero Starting Value | 649 |

|    |      | 11.4.3 Setting the Timer Compare Alarm(s)             | 649 |

|    |      | 11.4.4 Starting the RTC Timer                         | 649 |

|    | 11.5 | Registers (RTCTMR)                                    | 650 |

|    | 11.6 | Registers (RTCCFG)                                    | 667 |

| 12 | Trus | t Protection Unit (TPU)                               | 671 |

|    | 12.1 | Registers (TPU)                                       | 672 |

|    | 12.2 | Registers (AES)                                       | 675 |

| 13 | CRC  | 16/CRC32 Engine                                       | 687 |

|    | 13.1 | Overview                                              | 687 |

|    | 13.2 | Prerequisites for Use                                 | 687 |

|    |      | 13.2.1 CRC Peripheral Clock Generation                | 687 |

MAX32630 Rev B User Guide

|      | 13.2.2 CRC Peripheral Clock Gating                         | 687 |

|------|------------------------------------------------------------|-----|

| 13.3 | 3 CRC16 Operation                                          | 688 |

|      | 13.3.1 Calculating CRC16-CCITT-FALSE On Big-Endian Data    | 688 |

|      | 13.3.2 Calculating CRC16-CCITT-FALSE On Little-Endian Data | 689 |

|      | 13.3.3 Calculating CRC16-CCITT-TRUE On Big-Endian Data     | 689 |

|      | 13.3.4 Calculating CRC16-CCITT-TRUE On Little-Endian Data  | 689 |

| 13.4 | 4 CRC32 Operation                                          | 690 |

|      | 13.4.1 Calculating CRC32 On Big-Endian Data                | 690 |

|      | 13.4.2 Calculating CRC32 On Little-Endian Data             | 691 |

| 13.5 | 5 Registers (CRC)                                          | 692 |

|      |                                                            |     |

### 14 Trademarks and Service Marks

## **1** Disclaimer and Revision History

## Disclaimer

#### LIFE SUPPORT POLICY

MAXIM'S PRODUCTS ARE NOT DESIGNED, INTENDED OR AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT, LIFE SUSTAINING, DEVICES OR SYSTEMS OR APPLICATIONS, INCLUDING BUT NOT LIMITED TO, NUCLEAR, TRANSPORTATION OPERATING SYSTEMS, IN WHICH THE FAILURE OF SUCH GOODS COULD REASONABLY BE EXPECTED TO RESULT IN PERSONAL INJURY, LOSS OF LIFE OR SEVERE PROPERTY OR ENVI-RONMENTAL DAMAGE WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF MAXIM INTEGRATED PRODUCTS, INC.

#### As used herein

Life support, life sustaining devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2016 by Maxim Integrated Products, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. MAXIM INTEGRATED PRODUCTS, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. MAXIM ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering or registered trademarks of Maxim Integrated Products, Inc. All other product or service names are the property of their respective owners.

## **Revision History**

| Version | Changes         | Date       |

|---------|-----------------|------------|

| 0       | Release to web. | 10-14-2016 |

## 2 Overview

## Introduction

The **MAX32630** User Guide is targeted to hardware, embedded firmware and application developers. This guide provides information on how to use and configure the **MAX32630** memory, peripherals and registers. For ordering information, complete feature sets, package information, and electrical specifications, refer to the MAX32630/MAX32631 data sheet.

## **Related Documents**

- ARM<sup>®</sup> Cortex<sup>®</sup>-M4F Technical Reference Manual available from www.arm.com

- MAX32630/MAX32631 data sheet

- See the product page for additional device information and links to available design resources; these may include items such as evaluation kits, reference designs, application notes, and device errata.

## **Devices Covered by This Guide**

This User Guide covers functionality common to both the **MAX32630** and **MAX32631** devices. For simplicity's sake, when the device being used is referred to in the text, it is referred to as **MAX32630**, even though the text applies equally well to the **MAX32631**.

The following functionality is specific to the **MAX32631** only and is not covered in this guide:

- MAA modular arithmetic accelerator

- PRNG pseudo-random number generator

For details on the above MAX32631 specific topics, refer to the User Guide Supplement document for the MAX32631.

## **Key Device Features**

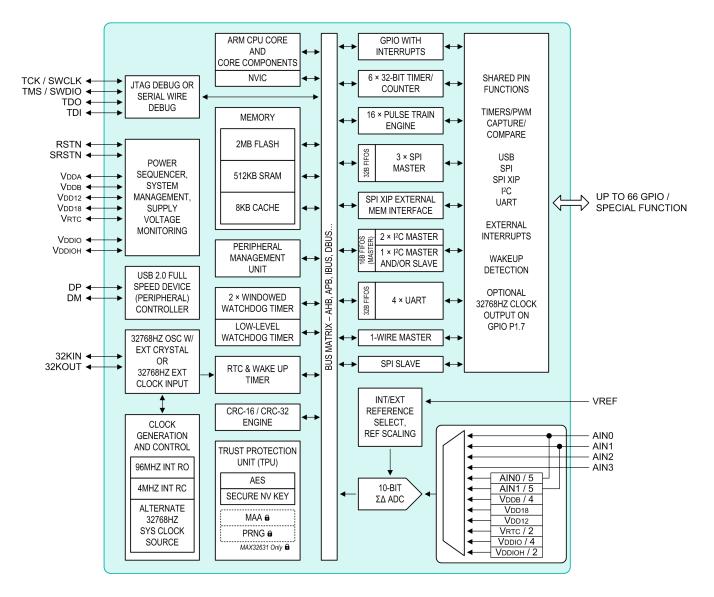

The **MAX32630** is a low-power, mixed signal microcontroller based on the 32-bit RISC ARM Cortex-M4F (M4 plus Floating Point Unit) CPU core with a maximum operating frequency of 96MHz.

Application code on the **MAX32630** runs from an onboard 2MB internal flash memory, with a 512KB SRAM available for general application use. An 8KB instruction cache improves execution throughput, and a transparent code scrambling scheme is used to protect customer intellectual property residing in the internal flash memory. Additionally, a SPI Execute In Place (XIP) external memory interface allows application code and data (up to 16MB) to be accessed from an external SPI memory device.

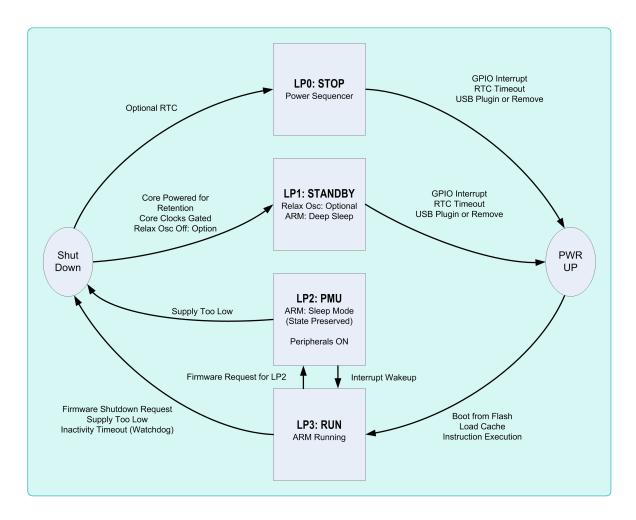

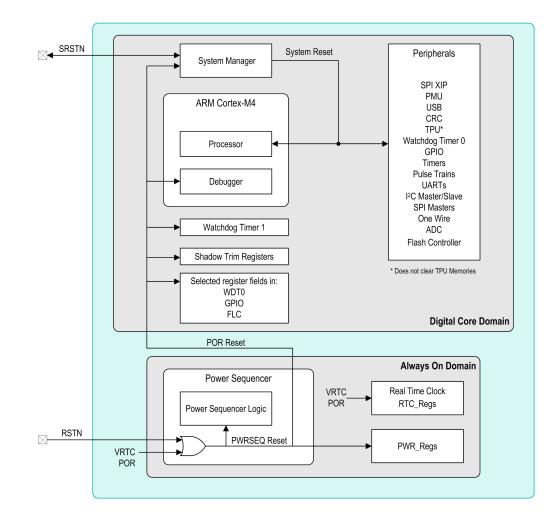

Four separate low-power operating modes - LP0:STOP, LP1:STANDBY, LP2:PMU, and LP3:RUN - allow the application to dynamically balance system power consumption against required processing capacity during different stages of operation. In the LP0:STOP and LP1:STANDBY modes, the CPU is in Deep Sleep mode (as defined in the ARM Cortex-M4 Devices Generic User Guide) and can be awakened (returning the system to LP3:RUN) by an enabled system wakeup event. In the LP2:PMU mode, the CPU is in Sleep mode, and can be awakened by an enabled NVIC interrupt request. In LP3:RUN, the CPU is actively executing application code. Refer to the device datasheet for details on power consumption under different low-power operating modes and peripheral configurations.

The **MAX32630** includes a 10-bit sigma-delta ADC with a multiplexer front end for four external input channels (two of which are 5.5V tolerant) and six internal channels. Dedicated divided supply input channels allow direct monitoring of onboard power supplies  $V_{DD12}$ ,  $V_{DD18}$ ,  $V_{DDB}$ ,  $V_{RTC}$ ,  $V_{DDIO}$  and  $V_{DDIOH}$  by the ADC. Built in limit monitors allow converted input samples from any channel to be compared against user-configurable high and low limits, with an option to trigger an interrupt and wake the CPU from the LP2:PMU low power mode if attention is required.

The **MAX32630** includes a wide variety of communications and interface peripherals, including a USB 2.0 slave interface, three master SPI interfaces, one SPI slave interface, four UART interfaces with hardware flow control and multi-drop support, three master I<sup>2</sup>C interfaces, a 1-Wire<sup>®</sup> master interface, and a slave I<sup>2</sup>C interface.

Sixteen independent pulse train engines allow hardware generation of square wave outputs or application-defined (from 2 to 32 bits in length) repeating waveform outputs on any GPIO pin. The application-defined waveforms from one or more pulse train engines can be synchronized, and each pulse train engine can be set to output its repeating waveform either indefinitely or for a number of iterations given by a loop counter. Any of the sixteen pulse train engines can be configured to begin generating its waveform when another pulse train engine reaches the end of its loop count, allowing pulse train output patterns to be chained back-to-back if needed.

Standard debug port functionality (using the JTAG or Serial-Wire Debug interfaces) is implemented to assist with application development.

Figure 2.1: MAX32630B Block Diagram

## 2.1 Core and Architecture

## 32-bit RISC ARM Cortex-M4F (M4 plus Floating Point Unit) Core

The **MAX32630** is based on the ARM Cortex-M4F 32-bit RISC CPU, which implements the ARMv7E-M architectural profile. The implementation of the ARM Cortex-M4F core used in the **MAX32630** is targeted for a maximum operating frequency of 96MHz and provides the following features.

- 32-bit data path with mixed 16-bit and 32-bit instructions (Thumb-2 instruction set)

- Single cycle multiply-accumulate (MAC) with 16/32-bit multiply operations and 32/64-bit accumulate operations

- DSP extensions include hardware division operation (2-12 cycles)

- Extended data processing instructions for SIMD (single instruction multiple data) operations, with dual 16-bit and quad 8-bit operations

- Single precision Floating Point Unit (FPU) extension for floating point arithmetic (IEEE® 754 compliant)

- Memory Protection Unit (MPU) for RTOS support

- Nested vectored interrupt controller (NVIC) with multiple interrupt priority levels and nested interrupt support

- Byte addressable memory space (accessed using 32-bit pointers), shared by code memory, data memory, and peripheral registers

- Low power, highly energy efficient core reduces power consumption

- Built-in debug functionality with JTAG port and Serial-Wire (SW) Debug interface (connects to internal Debug Access Port)

- Power saving Sleep and Deep Sleep modes

#### 2.1.1 Core Parameters

When the ARM Cortex-M4F core is included in a design, values must be selected for configurable parameters in the core. For the **MAX32630** design, key ARM Cortex-M4F core configuration parameters are shown below.

| Parameter       | Value | Description                                                                                                                                                              |

|-----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUM_IRQ         | 64    | The NVIC on this device is configured to support a maximum of 64 device-specific interrupt vectors. Not all of these vectors are used on the device.                     |

| LVL_WIDTH       | 3     | Specifies the number of bits of interrupt priority levels supported. This device uses a width of three, which means there are eight interrupt priority levels supported. |

| MPU_PRESENT     | 1     | The MPU (memory protection unit) is included on this device, with 8 protection regions defined.                                                                          |

| BB_PRESENT      | 1     | Bit-banding (memory mapped bit) operations are supported on this device.                                                                                                 |

| DEBUG_LVL       | 3     | Full debug with data matching. All debug functionality is present including data matching for watchpoint gen-<br>eration.                                                |

| TRACE_LVL       | 0     | No trace functionality included. ITM, TPIU, ETM and HTM are not present.                                                                                                 |

| RESET_ALL_REGS  | 1     | CPU core registers are set to a known state when the device exits reset.                                                                                                 |

| JTAG_PRESENT    | 1     | This device implements the JTAG Debug Access Port.                                                                                                                       |

| CLKGATE_PRESENT | 1     | Architectural gates are included to minimize dynamic power dissipation.                                                                                                  |

| FPU_PRESENT     | 1     | This device includes Floating Point Unit (FPU) functionality.                                                                                                            |

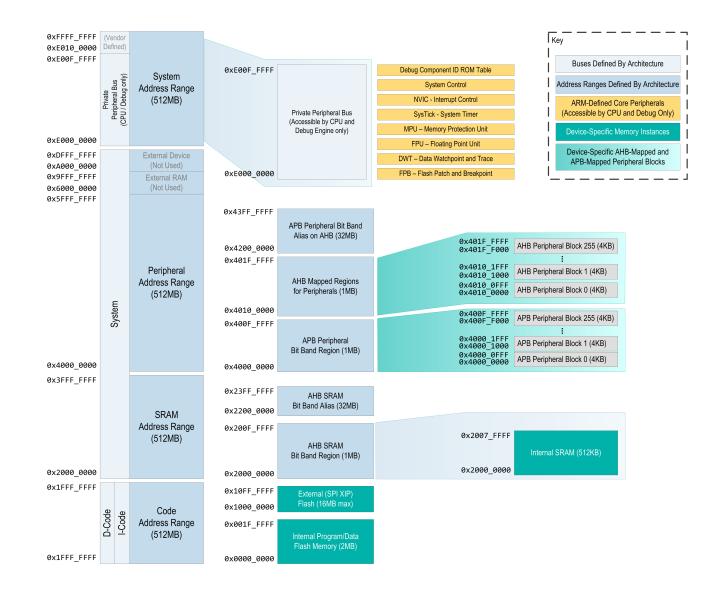

#### 2.1.2 Generic Memory Map

Figure 2.2: Memory Map

#### 2.1.3 AHB Buses

The standard ARM Advanced High Performance Bus (AHB-Lite version) is used for several different system bus masters on the **MAX32630**. All buses are 32 bits in width.

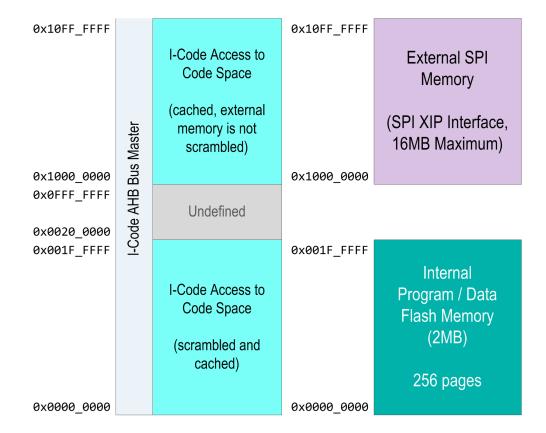

- I-Code: Performs instruction fetches from internal code memory regions. On the MAX32630, instruction fetches from internal flash memory (and external SPI XIP memory if enabled) can be cached to improve execution throughput.

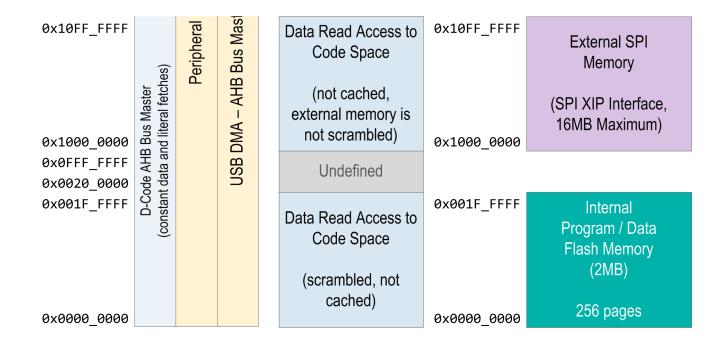

- **D-Code**: Performs data fetches from internal flash memory (and external SPI XIP memory if enabled); this includes literal local constant fetches. These data fetches cannot be cached, unlike instruction code fetches.

- System: Performs instruction fetch, data read/write and bit band operations on internal SRAM, and data read/write (including bit band) operations on peripherals. Instruction and data fetches on the System bus cannot be cached. Bit band remapping is performed for data accesses to internal SRAM only; instruction fetches are not affected by bit band aliasing.

- Note Bit band operations are translated internally by the CPU into a read-modify-write sequence, and so only the CPU and the debug port can read or write to locations using the bit banding function. The bit banding alias areas, although they are shown on the memory map, do not exist as separate logical mapped areas, and so they cannot be accessed by other AHB masters (such as the PMU) since they do not exist at this layer.

Peripherals which require higher speed access for large data transfers have control/buffer interfaces mapped to the AHB bus in the region from address 0x4010\_0000 to 0x401F\_FFFF. These AHB interface regions are designed to allow more rapid data transfer directly through the AHB bus, without having to go through the AHB-to-APB bridge. Unlike the peripheral registers (which are accessed through the AHB-to-APB bridge), an AHB interface region for a peripheral may be accessed in 8-bit, 16-bit, or 32-bit memory widths, if the peripheral supports this. Peripherals using this type of interface include SPI master, I<sup>2</sup>C master, UART, ADC, AES, CRC, and USB.

#### 2.1.4 APB Buses

The majority of the digital and analog peripherals on the **MAX32630** are controlled by registers that are memory mapped into the standard Peripheral region, from address  $0 \times 4000\_0000$  to  $0 \times 400F\_FFFF$  (in the bit banding enabled region). These peripherals are connected to the CPU core using a lower-speed APB peripheral bus (connected to the System AHB-Lite bus through an AHB-to-APB bridge). This improves overall system performance by reducing the amount of time that the AHB spends waiting for slower peripherals to complete register read or write operations.

Note The APB bus supports 32-bit width access only. All access to the APB peripheral register area (from 0x4000\_000 to 0x400F\_FFF) *must* be 32-bit width only with 32-bit (4 byte) alignment. Access using 8-bit or 16-bit width to this memory region is not supported and will result in an AHB memory fault exception (returned by the AHB-to-APB bridge interface). Bit band operations in Peripheral space are not affected by this restriction, because the CPU translates these accesses into 32-bit read or read-modify-write operations.

#### 2.1.5 Private Peripheral Bus (CPU Core Internal)

The Private Peripheral Bus (PPB), which includes both AHB and APB segments, is a dedicated bus internal to the ARM CPU core. This bus is accessible by the CPU and debug port only; it cannot be accessed by other AHB masters such as the Peripheral Management Unit.

The PPB provides access to a number of ARM Cortex-M4F core components:

- ROM table containing component and device identification for use by the debugger

- System Control registers

- NVIC (Interrupt control)

- System Timer (SysTick)

- Memory Protection Unit (MPU)

- Floating Point Unit (FPU)

- Data Watchpoint and Trace (DWT)

- Flash Patch and Breakpoint (FPB)

#### Note The MAX32630 does not support trace functionality, which means that the DWT component is used for watchpoints only in this implementation.

For more information on these core components, refer to the ARM technical documentation for the ARM Cortex-M4F.

There is an additional External PPB (private peripheral bus) which is a 32-bit bus based on the APB (Advanced Peripheral Bus) standard. It is intended for adding components to the private peripheral bus area which are not intended for general application use, since privileged operating mode is required to access this area. The **MAX32630** does not map any additional components to this bus area.

#### 2.1.6 Nested Vectored Interrupt Controller (NVIC)

The **MAX32630** includes the standard Nested Vectored Interrupt Controller (NVIC) as implemented for the ARM Cortex-M4F core. The NVIC supports high speed, deterministic interrupt response, interrupt masking and multiple interrupt sources. External interrupts support rising or falling edge trigger mode, as well as level triggered mode.

With the core instantiation parameters given above, the NVIC supports a maximum of 64 device-specific interrupt vectors. The **MAX32630** uses interrupt vectors 0 to 41. Programmable interrupt priority is supported, allowing up to eight priority levels to be used (3-bit width for priority field).

Note Some device-specific interrupt vectors may include more than one potential interrupt source, and certain device-specific interrupt vectors in the range 0.. 41 may be reserved. Refer to the Interrupt Vector Table section for more details.

#### 2.1.7 Debug

The **MAX32630** includes the standard JTAG debug engine as implemented for the ARM Cortex-M4F core. The JTAG TAP interface is supported, along with the reduced-pin-count Serial-Wire Debug Interface.

There are two JTAG TAP device addresses for the **MAX32630**. The address for the ARM Debug, first in the JTAG chain, is 0x4BA0\_0477; the address for the Maxim Test JTAG, second in the JTAG chain, is 0x07F7\_6197. The Maxim Test JTAG is intended for Maxim internal testing and characterization purposes only. It is mentioned here only to avoid confusion between it and the ARM Debug JTAG TAP, and also for reference in the event that both JTAG TAPs in the chain need to be bypassed.

Note Security restrictions enforced on the Maxim Test JTAG are similar to those enforced on the ARM Debug JTAG interface. If debug access is locked out due to security settings, the ability of the Maxim Test JTAG to access internal device memory and peripheral registers will be locked out as well.

Standard features supported by the ARM debug engine include the ability to set up to six instruction breakpoints (as well as two data literal breakpoints and four data watchpoints), access memory areas and peripheral registers even when the CPU is running, and pause or reset the CPU. When the CPU is in the paused state, instructions may be executed in single-step mode.

Note The debug engine is coupled to the CPU only for clocking and reset purposes. If the debug engine pauses the CPU, this does not pause other peripherals and functions on the MAX32630, which will continue to operate normally.

#### 2.1.8 Trace

The MAX32630 does not support application tracing or trace port functionality.

## 2.2 Power Supplies and Modes

#### 2.2.1 Supply Voltages

The following digital and analog supply voltages are used by the **MAX32630**. These are typically provided by an external power management IC (PMIC). The **MAX32630** does not include internal regulators to derive lower-voltage external supplies from higher-voltage external power supplies; this functionality (along with battery supply management and battery charging functions) is intended to be provided by the companion PMIC device.

Note One exception is the internal retention regulator; however, this regulator is limited to certain predefined uses relating to device state retention during LP1:STANDBY. It cannot be used to replace any of the main external power supplies while the device is in the active modes LP2:PMU or LP3:RUN.

#### 2.2.2 V<sub>DD18</sub> (Nominal 1.8V) Digital Power Supply

This digital power supply is used to power the internal flash memory, comparators used for power supply monitoring, the two relaxation oscillators on the **MAX32630**, and certain power management and monitoring functions.

#### 2.2.3 V<sub>DDIO</sub> (1.8V to 3.6V) I/O Power Supply

This digital power supply is used by default to power the I/O drive circuitry for all GPIO pins on the device. GPIO pins can be switched on an individual basis between  $V_{DDIO}$  and the alternate GPIO supply  $V_{DDIOH}$ .

#### 2.2.4 V<sub>DDIOH</sub> (1.8V to 3.6V) I/O Power Supply

This digital power supply can be used as an alternate power source for the I/O drive circuitry for one or more GPIO pins on the device. The use of the  $V_{DDIOH}$  power supply is optional, but if used,  $V_{DDIOH}$  must be equal to or higher than  $V_{DDIO}$ . GPIO pins can be switched on an individual basis between  $V_{DDIO}$  and the alternate GPIO supply  $V_{DDIOH}$ .

#### 2.2.5 V<sub>DD12</sub> (Nominal 1.2V) Digital Power Supply

This digital power supply is used to power most of the digital logic on the **MAX32630**, including the CPU core, flash memory, SRAM, the 4MHz RC oscillator, and digital peripherals. This is also the default power source used by the retention regulator.

#### 2.2.6 V<sub>RTC</sub> (Nominal 1.8V) RTC Power Supply

This power supply is used to maintain functions on the **MAX32630** that must continue operating under all power management modes. It is used to power the 32.768kHz RTC oscillator, the 8kHz nanoring oscillator, and 'always-on' functions including the Real Time Clock, the power sequencer, and power management functions including the retention controller.

If the V<sub>RTC</sub> supply drops below the VRTC POR level, all registers and functions on the entire device will be reset, including the Real Time Clock and power sequencer.

#### 2.2.7 V<sub>DDA</sub> (Nominal 1.8V) Analog Power Supply

This power supply is used by analog functions included in the ADC and analog front end. These analog functions include the ADC itself, analog input multiplexing, internal reference generation, and internal/external reference selection. The V<sub>DDA</sub> supply is also used by some power management functions and to generate internal comparison reference levels used for power supply monitoring. For this reason, V<sub>DDA</sub> must always be powered, even if the ADC is not being used by the application.

#### 2.2.8 V<sub>DDB</sub> (Nominal 3.3V) USB Power Supply

This power supply (used by the USB PHY and related functions) must be provided at the V<sub>DDB</sub> pin since the **MAX32630** does not include an internal USB supply regulator.

#### 2.2.9 Low-Power Modes

The **MAX32630** supports 4 major power modes which are user configurable to application specific needs. State-specific configuration details are stored in always on power domain registers that are continuously powered across all modes of operation. Firmware-controlled power gating and hardware-controlled clock gating of peripherals allow designers to optimize system power consumption. The 4 power modes supported are LP0:STOP (with or without RTC), LP1:STANDBY (with data retention), LP2:PMU (ARM asleep) and LP3:RUN (ARM active).

For more details on the low-power modes, refer to the Power Ecosystem and Operating Modes section.

#### 2.2.10 Power Supply Monitoring

The **MAX32630** includes a set of supply voltage monitors which compare power supply levels on the device against predefined reset thresholds. Depending on application requirements, these supply voltage monitors can be configured to trigger interrupts when a power supply failure is detected, or the power supply status can simply be monitored by application firmware using SVM event status bits. For certain power supplies, the power sequencer can be configured to trigger a Power-On Reset for the entire system when a power supply failure is detected.

For more details, refer to the Power Ecosystem and Operating Modes section.

## 2.3 Clock Sources

#### 2.3.1 Internal 96MHz Relaxation Oscillator

The **MAX32630** includes a high-frequency internal relaxation oscillator designed to operate at a nominal frequency of 96MHz. The output of this relaxation oscillator is the default primary system clock source for most digital logic on the device.

The MAX32630 does not support operation from an external high-frequency crystal.

#### 2.3.2 Internal 4MHz RC Oscillator

For applications or situations where less processing power is needed, the **MAX32630** provides an 4MHz internal RC oscillator which can be used as an alternate primary clock source. When the 4MHz RC oscillator mode is enabled, the 4MHz oscillator output is used as the primary clock source, instead of the 96MHz internal relaxation oscillator output.

#### 2.3.3 Internal 44MHz Relaxation Oscillator (Crypto Oscillator)

A secondary high-frequency internal relaxation oscillator, targeted to run at a nominal frequency of 44MHz, is also available. This internal relaxation oscillator is also known as the Crypto Oscillator. The output of this relaxation oscillator is used as a secondary timing source for cryptographic functions in the TPU including the PRNG (**MAX32631** only), the AES engine, and the MAA (**MAX32631** only). This increases security and makes certain types of timing-based attacks and power-analysis-based attacks against the TPU more difficult, due to the fact that certain internal cryptographic operations are driven by this secondary, non-observable clock.

The Crypto Oscillator cannot be used as a primary system clock source; it is reserved for use by TPU functions only.

#### 2.3.4 RTC 32768Hz Crystal Oscillator

The **MAX32630** includes a 32768Hz crystal oscillator circuit, which requires an external 32.768kHz crystal to be connected between the 32KIN and 32KOUT pins as detailed in the **MAX32630** datasheet. This oscillator is used to generate the 32768Hz clock which is used by the Real Time Clock.

An external clock source may also be used in place of the 32768Hz crystal oscillator. When using this configuration, the 32.768kHz crystal is not used. Instead, the external clock source (which must meet the electrical/timing requirements given in the datasheet) is connected to the 32KIN pin, and the 32KOUT pin is left unconnected.

The 32768Hz clock is required in order to meet USB timing standards, because this clock is used for internal frequency calibration of the 96MHz relaxation oscillator. This means that if the application will be using the USB interface, either a 32.768kHz external crystal must be installed between the 32KIN and 32KOUT pins, or a 32.768kHz external clock source must be connected to the 32KIN pin. As detailed in the **MAX32630** datasheet, when a 32.768kHz external clock source is connected to the 32KIN pin, the 32KOUT pin must be left unconnected.

When the crystal oscillator is running, the 32768Hz output clock can optionally be driven to port pin P1.7. Refer to Enabling 32768Hz Oscillator Output on P1.7 for details.

For applications which can operate properly at very low processing rates, the 32.768kHz clock can also be used as a primary system clock source. This will reduce active operating current to a much lower level. When using this option, however, most functions and digital peripherals on the device (exceptions include the TPU-based functions and the watchdogs) will have their operating speed limited to a maximum of 32.768kHz as well. This means that certain peripherals with a specification including a minimum speed requirement (such as USB) will not be usable.

## 2.4 Memory

All memory regions on the MAX32630 (including memory-mapped register areas) are implemented in little-endian format.

#### 2.4.1 Internal Flash Memory

The **MAX32630** includes 2MB (or 512K x 32 bits) of internal flash memory. This internal flash memory may be used to store application program code as well as constant static data used by application code. Locations in the internal flash memory are programmed one doubleword (32 bits) at a time. Once an internal flash memory location has been programmed, it must be erased before it can be reprogrammed to a different value.

The internal flash is divided into 256 pages of 8KB (or 2048 x 32 bits) each. When erasing data in internal flash memory, it is not possible to erase a single doubleword (32-bit) location independently. Instead, the flash contents may be erased either by erasing a single flash memory page at a time (page erase), or by erasing the entire internal flash memory at once (mass erase). Erased (blank) locations in the internal flash memory will always read as all ones (value 0xFFF\_FFF).

Modifications to the flash memory array (either program or erase operations) are handled by the Flash Controller (FLC).

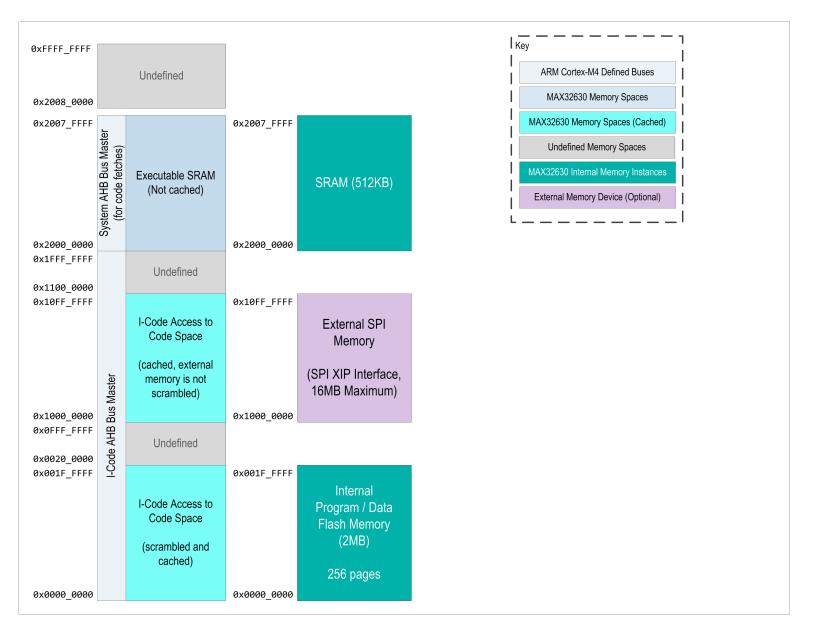

For read access, the internal flash memory is mapped into the standard code/data space region beginning at address 0x0000\_0000. The internal flash memory is accessed via the AHB, and so 8-bit, 16-bit and 32-bit read access widths are supported.

The beginning of internal flash memory (starting at address 0x0000\_0000) is also the default location for the ARM exception/interrupt vector table. Since this table contains initialization information (such as the reset vector address) which is required for the system to properly initialize, this table must be loaded into the internal flash memory in order for the **MAX32630** to execute any application code.

#### 2.4.2 8KB Instruction Cache

The 8KB (2048 x 32 bits) instruction cache is used to store CPU instructions that have been recently fetched from locations in the internal flash memory (or external SPI XIP memory, if enabled). By avoiding repeated refetches of frequently accessed code, the instruction cache helps to improve execution throughput. Instruction fetches from the ARM CPU are handled by the instruction cache, which either returns the previously cached instructions (cache hit), or fetches the requested data from the internal flash (cache miss) and stores it for future access. Fetches between the instruction cache and the internal flash memory go through the code descrambler, so that the content stored in the instruction cache has already been descrambled. If the external SPI XIP flash memory interface is being used, instruction fetches from the external SPI flash memory are also cached in the same manner as instructions fetched from the internal flash memory. However, unlike content stored in the internal flash memory, content stored in the external SPI flash memory is not scrambled.

Code access to the internal data SRAM is not cached; for this type of access, instructions are always fetched directly from the SRAM.

When data is read from the internal flash memory (D-Code fetches, as opposed to I-Code fetches for the purposes of decoding instructions), this data is fetched directly from the internal flash. This includes fetches of local constant literals that are used by certain ARM instruction op codes.

Firmware has the ability to flush the instruction cache manually at any point using the ICC\_INVDT\_ALL register. After code mapped into a cached instruction space is updated (for example, if an in-application programming modification is made to an executable area of internal flash memory or external SPI XIP flash memory), firmware must flush the cache to ensure that the latest version of the code will be accessible and that stale cache contents will not be used instead of the new flash programmed values.

Note By default, the instruction cache is disabled following any system reset. For proper operation, the application must explicitly enable the instruction cache following system startup. Refer to the Instruction Cache Controller Operations and Recommended Settings to be Written At Application Startup sections for more details.

#### 2.4.3 Internal SRAM

The internal SRAM on the **MAX32630** is 512KB in size and has a 32-bit internal width. It is mapped into the SRAM bit-banding access region beginning at address 0x2000\_0000, and so it can be read and written either 8/16/32 bits at a time using the standard AHB interface, or a single bit at a time using the ARM-defined bit-band alias region (beginning at address 0x2200\_0000).

The bit-banding function can only be used when the SRAM is being accessed in data space by the ARM core itself, since the ARM core handles the remapping from the bit-banding alias area to a read-modify-write sequence (or single read/mask/shift for a bit read function) of the standard memory area.

The SRAM can be read from or written to in data space by application firmware, and can be used for either code or data access. The SRAM is also used to hold the ARM CPU stack.

The contents of the SRAM are indeterminate following initial system powerup. SRAM state is maintained during LP3:RUN, LP2:PMU, and LP1:STANDBY only.

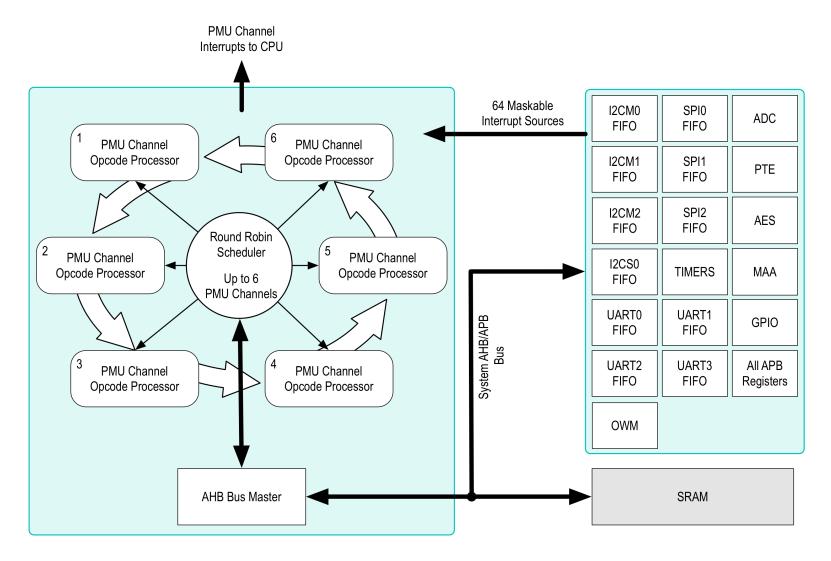

#### 2.4.4 Peripheral Management Unit (PMU)

The Peripheral Management Unit (PMU) is a programmable state machine that can perform DMA operations in SRAM and control multiple peripherals without using the CPU, thereby significantly improving overall system power consumption in LP2:PMU. It provides flexible mechanisms to perform automatic read and/or write sequences to peripherals and areas of internal SRAM and is capable of operation in LP2:PMU and LP3:RUN power modes.

Some peripherals include dedicated memory areas and/or transmit/receive FIFOs which are mapped to the AHB bus for high-speed access. The PMU is specifically optimized to perform DMA data transfer operations involving these AHB-mapped memory regions. Peripheral types which provide this type of interface include:

- ADC

- UART

- SPI Master

- I<sup>2</sup>C Master

- USB (Endpoint buffers are stored in the main SRAM area)

- CRC

- AES

- MAA (**MAX32631** only)

The PMU controller can read from the internal flash memory and the external SPI XIP flash memory (if enabled). It can read from and write to the internal SRAM and any peripheral register area which can be accessed on the System bus.

#### 2.4.5 Info Block

The flash information block (also referred to as the info block) on the **MAX32630** allows production trim values and other nonvolatile information that will be written during the production process (e.g., device configuration and test details / logging data) to be stored in a separate dedicated area of internal flash memory.

The mapping location for the info block is in the code space area, beginning at byte address location 0x0020\_0000 (which is immediately following the highest internal flash memory address). When the info block is mapped to this memory region, it can be accessed in the same manner as the main flash. That is, it can be read from in code space, although accesses to it are not cached under any circumstances, and its contents are not scrambled. It is possible to write to locations in the info block using the flash controller registers.

However, this mapping of the info block (and direct read/write access to its contents) is only intended for testing and trimming purposes during the factory production test sequence. Once production test of the **MAX32630** has completed, a lock option setting is set in the info block to prevent future modifications to the trim and option settings. Setting the info block lockout setting also removes the info block from the memory map, which means that the only way to view its contents after that point is by reading the copies of the info block settings that have been copied into the trim shadow registers. These registers are mapped to a different area in the APB peripheral region.